ابتكرت مجموعة من الباحثين في قسم الإلكترونيات والمعلومات والهندسة الحيوية في Politecnico di Milano شريحة جديدة تهدف إلى تقليل استهلاك الطاقة بشكل كبير مع تسريع معالجة كميات كبيرة من البيانات.

نُشرت نتائج هذا العمل في مجلة Nature Electronics، وقد قاد المشروع الأستاذ Daniele Ielmini، وكان الباحث Piergiulio Mannocci هو المؤلف الأول للورقة العلمية.

تسريع العمليات الحسابية مع استهلاك طاقة أقل

جاء هذا الابتكار ضمن مشروع ANIMATE (ANalog In-Memory computing with Advanced device TEchnology)، الذي استند إلى أبحاث Ielmini السابقة حول CL-IMC (Closed-Loop In-Memory Computing)، والتي تهدف إلى تسريع العمليات الحسابية مع استهلاك طاقة أقل يصل إلى 5000 مرة مقارنة بأجهزة الكمبيوتر الرقمية التقليدية.

تعتمد الشريحة على الحوسبة داخل الذاكرة، والتي تتغلب على قيود نقل البيانات المستمر بين الذاكرة والمعالج، ما يجعل الأنظمة أسرع وأكثر كفاءة في استخدام الطاقة.

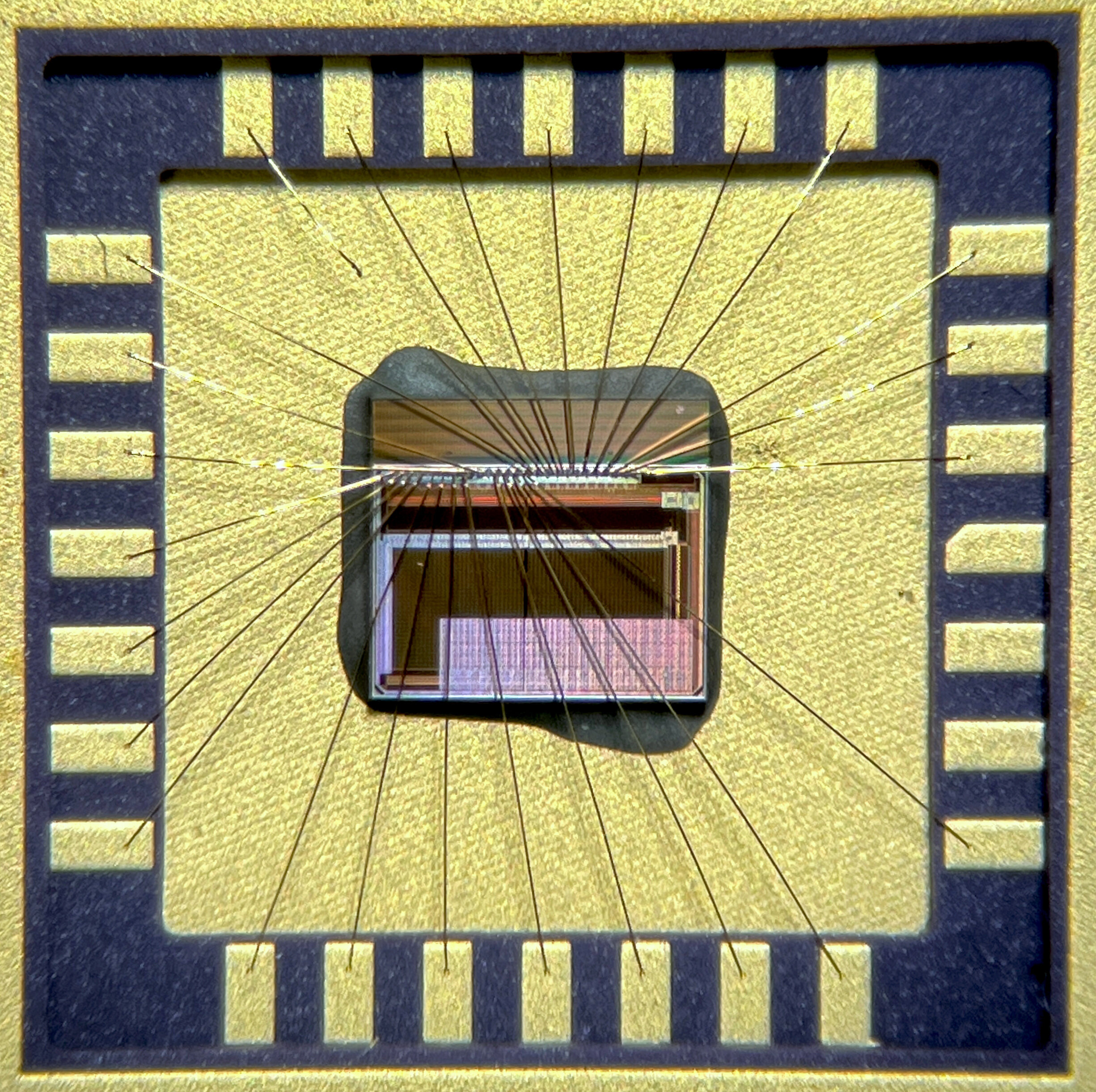

الشريحة المتكاملة تم تصميمها لمعالجة الأنظمة الخطية وغير الخطية من المعادلات باستخدام تقنية CMOS المعيارية لإنتاج دوائر السيليكون المتكاملة.

يحتوي الجهاز على مصفوفتين قابلتين للبرمجة بحجم 64×64 من الذاكرة المقاومة، تعتمد على SRAM مع مقاومات مدمجة لتوفير مستويات مقاومة مختلفة.

كما يكمل البنية نموذج مبتكر للمعالجة التناظرية باستخدام مكونات مدمجة مثل المضخمات العملية ومحولات التناظر إلى رقمية.

التطبيق في الذكاء الاصطناعي

تتيح هذه البنية للشريحة معالجة العمليات المعقدة مباشرة في الذاكرة، مما يقلل زمن الحساب ويخفض استهلاك الطاقة، مع الحفاظ على دقة مشابهة للأنظمة الرقمية التقليدية وبحجم أصغر على السيليكون.

أوضح Ielmini “الشريحة المتكاملة تثبت إمكانية تطبيق الحوسبة التناظرية داخل الذاكرة على نطاق صناعي، نحن نعمل حاليًا على تطبيق هذا الابتكار في مجالات حقيقية لتقليل تكلفة الطاقة، خصوصًا في الذكاء الاصطناعي.”

وقال Mannocci “هذا العمل نتاج تعاون دولي بين الأكاديميا والصناعة، ويظهر إمكانيات الحوسبة التناظرية داخل الذاكرة للتطبيقات عالية الأداء وموفرة للطاقة.”

يمثل هذا الابتكار خطوة مهمة نحو أجهزة أكثر سرعة وكفاءة، مع إمكانيات واسعة في الذكاء الاصطناعي، معالجة البيانات الكبيرة، أنظمة الاتصالات الحديثة، والروبوتات، بالإضافة إلى شبكات الاتصالات المتقدمة مثل الجيل الخامس والسادس (5G و6G).